XHMC IP — 实现过程中可能会出现时序错误

发布时间:2018/3/8

描述

发现问题的版本:情况 1 的 XHMC IP v1.0 和情况 2 的 XHMC IP v1.0 (Rev .4)

解决问题的版本: 查看 (Xilinx 答复 67969)

有两种情况,XHMC IP 在实现过程中可能会遇到时序错误问题。

情况 1:

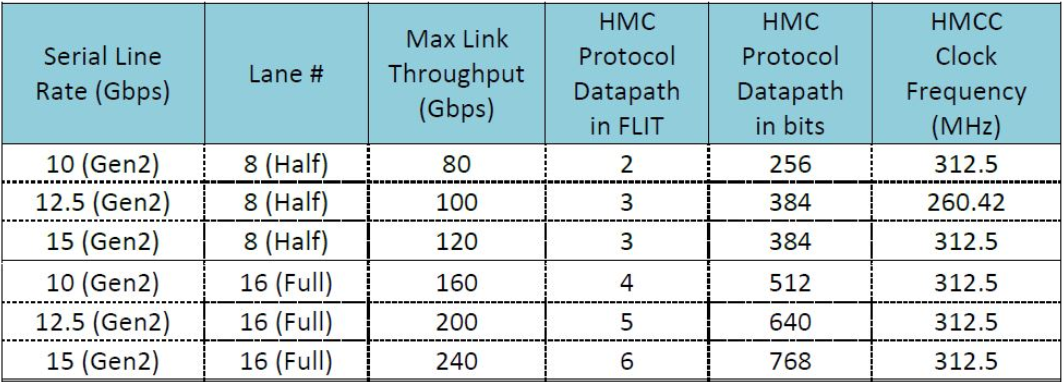

如果不使用推荐的 HMC 协议数据路径宽度,可能就会出现时序错误。请参考 HMC IP 用户指南,了解更多详情。

建议在 IP GUI 中使用以下数据路径宽度 (FLIT),确保在 Vivado 中满足时序要求:

情况 2:

在一些罕见的情况下,在 XHMC 设计中可能会沿着包含 BRAM 的路径出现时序错误。

解决方案

情况 1:

如果由于路由阻塞或设备利用率高而仍无法满足时序要求,您可能需要使用一个以下选项:

- 使用不同的时序收敛策略(例如探索)

- 使用“-extraNetDelay_high”实现选项

- 进一步增加数据路径宽度,以缓和时序收敛问题。

情况 2:

这些沿着包含 BRAM 的路径出现的时序错误由在设计中插入的 Vivado 电源优化逻辑路径引起。

该问题可通过沿 BRAM 时序路径禁用电源优化逻辑来解决。

下面是一个排除故障路径的实例:

set_power_opt -exclude_cells [get_cells -hier -filter {NAME =~ *genblk_pload_mem_inst.u_resp_pload_mem/genblk_block_ram_model.the_bram_reg_*}]修订历史::

- 10/05/2016 - 初始版本

- 2017 年 9 月 15 日 — 针对 BRAM 时序路径问题进行了更新